![]()

작성일: 2015.12.28

VHDL Examples (from Bejoy Thomas blog)...

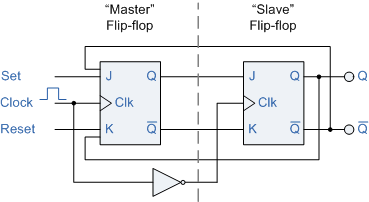

Master Slave JK Flip Flop

library ieee; use ieee.std_logic_1164.all; entity master_slave_jk is port(j,k,clk:in std_logic;q1,q1x,z1x:inout std_logic; q2,q2x,z2x: inout std_logic); end master_slave_jk; architecture arc of master_slave_jk is begin process(clk) begin if clk='1' then z1x<=(j and (not q2)) or ((not k)and q2); q1<=z1x after 5 ns; q1x<=not z1x after 5ns; else z2x<=(q1 and (not q2)) or ((not q1x)and q2); q2<=z2x after 5 ns; q2x<=not z2x after 5ns; end if; end process; end arc;

| Inputs | Output | Comments | ||

|---|---|---|---|---|

| J | K | C | Q | |

| 0 | 0 | High | Q0 | No Change |

| 0 | 1 | High | 0 | RESET |

| 1 | 0 | High | 1 | SET |

| 1 | 1 | High | /Q0 | Toggle |

VHDL code for Odd Parity Generator

library ieee; use ieee.std_logic_1164.all; entity bejoy_op is port(x,y,z:in std_logic; p:out std_logic); end bejoy_op; architecture a of bejoy_op is begin p<=((x xor y) xor z); end a;

VHDL code for Even Parity Generator

library ieee; use ieee.std_logic_1164.all; entity bejoy_ep is port(x,y,z:in std_logic; p:out std_logic); end bejoy_ep; architecture a of bejoy_ep is begin p<=((x xor y) xnor z); end a;

VHDL code for JK Flip Flop

library ieee; use ieee.std_logic_1164.all; entity bejoy_jkff is port(j,k,clk:in std_logic;q,q1,z:inout std_logic); end bejoy_jkff; architecture arc of bejoy_jkff is begin process(clk) begin if clk='1' then z<=(j and (not q)) or ((not k) and q); q<=z after 5ns; q1<=not z after 5ns; end if; end process; end arc;

VHDL code for T Flip Flop

library ieee; use ieee.std_logic_1164.all; entity bejoy_tff is port(t,clk:in std_logic;q,q1,z:inout std_logic); end bejoy_tff; architecture arc of bejoy_tff is begin process(clk) begin if clk='1' then z<=((t and (not q)) or ((not t) and q)); q<=z after 5ns; q1<=not z after 5ns; end if; end process; end arc;

VHDL code for SR Flip Flop

library ieee; use ieee.std_logic_1164.all; entity bejoy_rsff is port(s,r,clk:in std_logic;q,q1,z:inout std_logic); end bejoy_rsff; architecture arc of bejoy_rsff is begin process(clk) begin if clk='1' then z<=s or ((not r) and q); q<=z after 5ns; q1<=not z after 5ns; end if; end process; end arc;

VHDL code for D Flip Flop

library ieee; use ieee.std_logic_1164.all; entity bejoy_dff is port(d,clock :in std_logic; Q:out std_logic); end bejoy_dff; architecture arc of bejoy_dff is begin process(clock) begin if clock'event and clock='1' then Q<=D; end if; end process; end arc;

VHDL code for 3x8 Decoder

library ieee; use ieee.std_logic_1164.all; entity bejoy_3x8 is port(a,b,c:in std_logic; d0,d1,d2,d3,d4,d5,d6,d7:out std_logic); end bejoy_3x8; architecture arc of bejoy_3x8 is begin d0<= (not a) and (not b) and (not c); d1<= (not a) and (not b) and c; d2<= (not a) and b and (not c); d3<= (not a) and b and c; d4<= a and (not b) and (not c); d5<= a and (not b) and c; d6<= a and b and (not c); d7<= a and b and c; end arc;

VHDL code for 8x3 Encoder

library ieee; use ieee.std_logic_1164.all; entity bejoy_8x3 is port(d0,d1,d2,d3,d4,d5,d6,d7:in std_logic; a0,a1,a2:out std_logic); end bejoy_8x3; architecture arc of bejoy_8x3 is begin a2<= d4 or d5 or d6 or d7; a1<= d2 or d3 or d6 or d7; a0<= d1 or d3 or d5 or d7; end arc;

VHDL code for 1x4 Demultiplexer using structural style

library IEEE; use IEEE.std_logic_1164.all; entity bejoy_1x4 is port(s1,s2,data_in : in std_logic; d1,d2,d3,d4 : out std_logic); end bejoy_1x4; architecture arc of bejoy_1x4 is component dmux port(sx1,sx2,d : in std_logic; z1,z2 : out std_logic); end component; begin dmux1 : dmux port map(s1,s2,data_in,d1,d2); dmux2 : dmux port map(not s1,s2,data_in,d3,d4); end arc; library ieee; use ieee.std_logic_1164.all; entity dmux is port(sx1,sx2,d :in std_logic; z1,z2: out std_logic); end dmux; architecture arc of dmux is begin z1 <= d and (not sx1) and (not sx2); z2 <= d and (not sx1) and sx2; end arc;

VHDL code for 1x2 Demultiplexer

library ieee; use ieee.std_logic_1164.all; entity bejoy_1x2 is port(d,s:in std_logic; z0,z1:out std_logic); end bejoy_1x2; architecture arc of bejoy_1x2 is begin z0 <= d and (not s); z1 <= (d and s); end arc;

VHDL code for 4x1 Multiplexer using structural style

library IEEE; use IEEE.std_logic_1164.all; entity bejoy_4x1 is port(s1,s2,d00,d01,d10,d11 : in std_logic; z_out : out std_logic); end bejoy_4x1; architecture arc of bejoy_4x1 is component mux port(sx1,sx2,d0,d1 : in std_logic; z : out std_logic); end component; component or_2 port(a,b : in std_logic; c : out std_logic); end component; signal intr1, intr2, intr3, intr4 : std_logic; begin mux1 : mux port map(s1,s2,d00,d01,intr1); mux2 : mux port map(not s1,s2, d10,d11,intr2); o1 : or_2 port map(intr1, intr2, z_out); end arc; library ieee; use ieee.std_logic_1164.all; entity mux is port(sx1,sx2,d0,d1 :in std_logic; z1,z2: inout std_logic; z: out std_logic); end mux; architecture arc of mux is begin z1 <= d0 and (not sx1) and (not sx2); z2 <= (d1 and (not sx1) and sx2); z<= z1 or z2; end arc; entity or_2 is port(a,b : in bit; c : out bit); end or_2; architecture arc of or_2 is begin c<=a or b; end arc;

VHDL code for 2x1 Multiplexer

library ieee; use ieee.std_logic_1164.all; entity bejoy_2x1 is port(d0,d1,s:in std_logic; z:out std_logic; z1,z2: inout std_logic); end bejoy_2x1; architecture arc of bejoy_2x1 is begin z1 <= d0 and (not s); z2 <= (d1 and s); z <= z1 or z2; end arc;

VHDL code for 4 bit Gray to Binary converter

library ieee; use ieee.std_logic_1164.all; entity bejoy_g2b is port( g:in std_logic_vector(3 downto 0); b:inout std_logic_vector(3 downto 0)); end bejoy_g2b; architecture a of bejoy_g2b is begin b(3)<=g(3); b(2)<=b(3) xor g(2); b(1)<=b(2) xor g(1); b(0)<=b(1) xor g(0); end a;

VHDL code for 4 bit Binary to Gray code converter

library ieee; use ieee.std_logic_1164.all; entity bejoy_b2g is port(b:in std_logic_vector(3 downto 0); g:out std_logic_vector(3 downto 0)); end bejoy_b2g; architecture a of bejoy_b2g is begin g(3)<=b(3); g(2)<=b(3) xor b(2); g(1)<=b(2) xor b(1); g(0)<=b(1) xor b(0); end a;

VHDL code for Full Subtractor

library ieee; use ieee.std_logic_1164.all; entity bejoy_fs is port(x,y,bi: in bit; b2,do,bo: out bit; d,b: inout bit); end bejoy_fs; architecture arc of bejoy_fs is begin d<=x xor y; b<=x and (not y); do<=bi xor d; b2<=bi and (not b); end arc;

VHDL code for Half Subtractor

library ieee; use ieee.std_logic_1164.all; entity bejoy_hs is port (x,y,en : in bit ; d,b : out bit; y1: inout bit); end bejoy_hs; architecture arc of bejoy_hs is begin process (en,y1) begin if en='1' then d<= x xor y; y1<= not (y); b <= x and y1; end if; end process; end arc;

VHDL code for Full Adder using structural style

library IEEE; use IEEE.std_logic_1164.all; entity bejoy_fa is port(In1,In2,c_in : in std_logic; sum, c_out : out std_logic); end bejoy_fa; architecture arc of bejoy_fa is component half_adder port(a,b : in std_logic; sum, carry : out std_logic); end component; component or_2 port(a,b : in std_logic; c : out std_logic); end component; signal s1, s2, s3 : std_logic; begin H1: half_adder port map(a=>In1, b=>In2, sum=>s1, carry=>s3); H2: half_adder port map(a=>s1, b=>c_in, sum=>sum, carry=>s2); O1: or_2 port map(a=> s2, b=>s3, c=>c_out); end arc; entity half_adder is port (a,b : in bit ; sum,carry : out bit); end half_adder; architecture arc of half_adder is begin sum<= a xor b; carry <= a and b; end arc; entity or_2 is port (a,b : in bit ; c : out bit); end or_2; architecture arc of or_2 is begin c<= a or b; end arc;

VHDL code for Half Adder

library ieee; use ieee.std_logic_1164.all; entity bejoy_ha is port (a,b : in bit ; s,c : out bit); end bejoy_ha; architecture arc of bejoy_ha is begin s<= a xor b; c <= a and b; end arc;

VHDL code for Basic Gates

AND Gatelibrary ieee; use ieee.std_logic_1164.all; entity and_gate is port (a,b : in std_logic ; c : out std_logic); end and_gate; architecture arc of and_gate is begin c <= a and b; end arc;OR Gate

library ieee; use ieee.std_logic_1164.all; entity or_gate is port (a,b : in std_logic ; c : out std_logic); end or_gate; architecture arc of or_gate is begin c <= a or b; end arc;NOT Gate

library ieee; use ieee.std_logic_1164.all; entity not_gate is port (a: in std_logic ; b : out std_logic); end not_gate; architecture arc of not_gate is begin b <= not a; end arc;NAND Gate

library ieee; use ieee.std_logic_1164.all; entity nand_gate is port (a,b : in std_logic ; c : out std_logic); end nand_gate; architecture arc of nand_gate is begin c <= a or b; end arc;NOR Gate

library ieee; use ieee.std_logic_1164.all; entity nor_gate is port (a,b : in std_logic ; c : out std_logic); end nor_gate; architecture arc of nor_gate is begin c <= a nor b; end arc;XOR Gate

library ieee; use ieee.std_logic_1164.all; entity xor_gate is port (a,b : in std_logic ; c : out std_logic); end xor_gate; architecture arc of xor_gate is begin c <= a xor b; end arc;

출처: http://blog.bejoythomas.com/search/label/VHDL%20Tutorial

![]()