NON-Synthesizable VHDL/Clock Generator

ИИРЯ PC ПЁ ЛчПыЕЩ ШИЗЮРЧ РЯКЮКаРЛ ФЈМТРИЗЮ МГАшЧв АцПь НУНКХл И№ЕЈРЧ РЯКЮКаРЛ КаЧвЧЯПЉ ЧеМК АЁДЩЧб МіСиРЧЗЮ БтМњЧЯИч РЬРЧ АЫСѕАњСЄПЁМ РЬРќ НУНКХл МіСиРЧ И№ЕЈРЛ ХзНКЦЎ КЅФЁЗЮМ ЛчПыЧвМі РжРЛАЭРЬДй.

НУЙФЗЙРЬМЧ И№ЕЈРК МГАшРЧ УжСО АсАњПЁ ДыЧб ХИРЬЙж АќАшИИРЛ БтМњЧбДй. ХИРЬЙж ЦЏМКРК VHDLРЧ delayПЁ РЧЧЯПЉ АЃДмЧЯАд БтМњЧвМі РжДй. ДйРНРК ХИРЬЙж И№ЕЈРЛ AFTER ПЁ РЧЧЯПЉ НБАд БтМњЧвМі РжРНРЛ КИПЉСиДй.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY delay IS

PORT ( a : OUT std_logic_vector(0 TO 3);

en : IN std_logic;

clk : OUT std_logic );

END delay;

ARCHITECTURE behave OF delay IS

SIGNAL clk_out : std_logic := '0';

BEGIN

function_genenerator :

PROCESS (en)

BEGIN

IF en='1' THEN

a <= "0000",

"0001" AFTER 20 ns,

"0010" AFTER 40 ns,

"0011" AFTER 60 ns,

"0100" AFTER 80 ns,

"0101" AFTER 100 ns,

"0110" AFTER 120 ns,

"0111" AFTER 140 ns,

"1000" AFTER 160 ns,

"1001" AFTER 180 ns,

"1010" AFTER 200 ns,

"1100" AFTER 220 ns;

ELSE

a <= "0000";

END IF;

END PROCESS;

clock_genenerator :

PROCESS

VARIABLE clk_time : INTEGER := 0;

BEGIN

WAIT FOR 10 ns;

IF clk_out = '0' THEN

clk_out <= '1';

ELSE

clk_out <= '0';

END IF;

END PROCESS;

clk <= clk_out;

END behave;

|

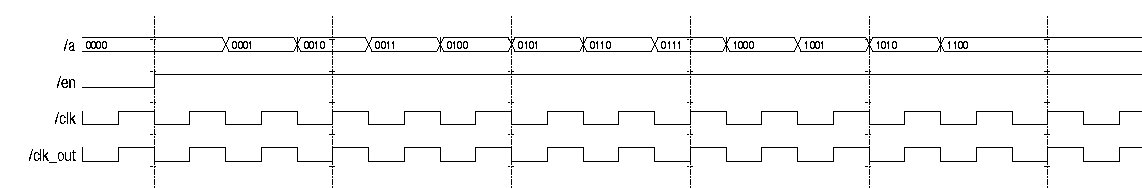

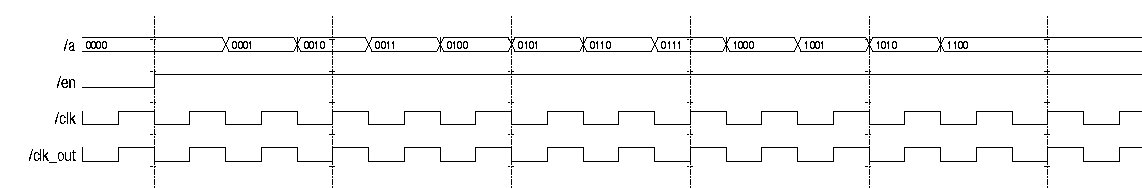

РЇРЧ ПЙДТ ClockАњ Function GeneratorРЬДй.

НУЙФЗЙРЬМЧ АсАњДТ,

РЬПЭААРК И№ЕЈРК ЧеМКЕЧСі ОЪДТДй. РЬЙЬ ИИЕщОюСј ЖѓРЬКъЗЏИЎЗЮ P&R ЧЯДТЕЅ ОюЖЛАд РгРЧРЧ delayИІ АЎДТ primitiveИІ МБХУЧв Мі РжАкДТАЁ? РЇПЭ ААРК И№ЕЈРК ХзНКЦЎ КЅФЁПЁ РЏПыЧЯАд ЛчПыЧвМі РжДй.

mailto:goodkook

CSA & VLSI Design Lab.